FPGA raktų pakabinto impulsų generatoriaus projektavimas: Sinchronizuojant impulsų plotį ir fazę

2024-12-17

5112

Katalogas

Įvadas

FPGA kūrimo srityje, kuriant tikslius pavienius impulsus, randami įvairūs pritaikymai.Šie impulsai kartais veikia be sinchronizacijos su laikrodžio ciklais, o tai leidžiama tik tada, kai nepastebimas labai tikslumas.Tačiau kai kurioms programoms impulsai reikalauja, kad impulsai puikiai atitiktų plotį ir fazę su laikrodžio ciklais, todėl reikia naudoti raktų pakabintą vieno impulso generatorių.Šie generatoriai, suaktyvinti pagal pagrindinę spaudą, siekia sukurti nuoseklius impulsus, pateikdami unikalius iššūkius, ypač laikrodžio sukelto virpėjimo įtaką FPGA lentoms.

Sinchronizacijos iššūkis

Rankiniai suaktyvinimo impulsai, kuriuos paveikė kintamieji, tokie kaip „Jitter“ dėl nenuspėjamo pagrindinio spaudos laiko pobūdžio, dažnai susiduria su techniniais iššūkiais.Pragmatiškas sprendimas yra disponavimo grandinės diegimas, sudėtingai sukurtas sutramdyti chaotiškus raktų įvestis.Ši grandinė efektyviai filtruoja triukšmą ir stabilizuoja įvesties signalus, skatindama stabilią vieno impulso generavimą.Realaus pasaulio programose inžinieriai išskiria išminties iš ankstesnės patirties, atskleisdami, kad įtraukiant šias grandines žymiai padidėja sistemos patikimumas.

Susidoroti su laikrodžio sukeltu virpėjimu

Laikrodžio sukeltas nerūpestingas kyla iššūkių, gali sutrikdyti impulsų laiką.Ši problema iškyla iš V ariat jonų laikrodžio laikotarpiu, kuris gali pakeisti tam tikrų užduočių būtiną laiką.Džiagų valdymas atsiranda dėl apgalvoto grandinės projektavimo ir veiksmingo FPGA išteklių panaudojimo.Subtilumas sumažinant virpėjimą užtikrina, kad impulsų generatoriai išlaikytų numatomą tikslumą.Atlikdami išsamų bandymą ir tikslų kalibravimą, ekspertai tiksliai sureguliuoja savo sistemas, užtikrindami, kad našumo standartai būtų pranokti.

Pažangios impulsų generavimo technikos naudojimas

Norint atlikti nepriekaištingą pulso generavimą, reikia pasirinkti sudėtingas metodikas.Technikos, tokios kaip kraštų aptikimas ir signalo kondicionavimas, naudojami impulsų ištikimybei sustiprinti.Tolesnis skolinimasis iš kognityvinių metodų, adaptyvūs algoritmai gali subtiliai stabilizuoti įvestis.Atsargus pažangių strategijų įgyvendinimas tyliai optimizuoja sistemos veikimą, išvengiant nereikalingo dėmesio.

Pagrindinis disponavimas ir vieno impulsų generatorius FPGA plėtroje

Dekonavimo grandinės kūrimas

Projektuojant veiksmingą pagrindinę diskonavimo grandinę, reikia protingo integruoti skaitiklį.Šis skaitiklis yra būtinas norint filtruoti atitraukiantį triukšmą, įtvirtinant įėjimo signalų stabilumą.Skaitymo dydis priklauso nuo numatomo „Jitter“ impulsų trukmės ir laikrodžio mėginių ėmimo dažnio sąveikos.Norint pritaikyti įprastus virvių periodus, identifikuotus nuo 5 iki 10 milisekundžių, galima atsižvelgti į 20 bitų skaitiklio modulį, įsigaliojantį su 24 MHz sistemos laikrodžiu.Tikslas yra įvesti vėlavimą artėjant 22 milisekundėms, užtikrinant tik nuoseklumo signalus pereiti, taigi tiksliai registruojant klavišus.Veikdama, aptikus pagrindinę presą, skaitiklis inicijuoja ir, įvykdydamas jo skaičių, atpažįsta pastovų signalą, palengvindamas saugų impulsų kūrimą.

Raktų kontroliuojamos vieno impulsų generatoriaus grandinės principas

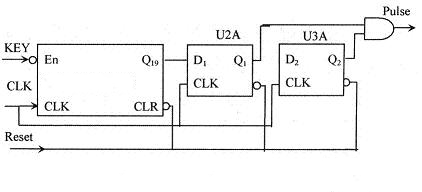

Key kontroliuojamas vieno impulsų generatorius naudoja aukščiau paminėtą grandinę, kad išspręstų pagrindinę diskonavimo problemą ir gautų stabilų signalą.Norėdami generuoti vieną impulsą, naudokite du D flip-flops ir an ir vartus, kaip parodyta 1 paveiksle.

„D flip-flop U2A“ suaktyvinamas gavus stabilų signalą D1 = 1.„FLIP-FLOP U2A“ Q1 terminalas gauna teigiamą impulsą, sinchronizuotą su CLK.Išėjimo q1-D Flip-Flop U3A, gaukite teigiamą impulsą, atidėtą vienu laikrodžio ciklu nei Q1, ir apverskite Q2 išėjimą, kad gautumėte neigiamą impulsą.Q1 ir QN2 išėjimai, kaip AN ir vartų įvestis, išves vieną impulsą, kurio impulso plotis yra dvigubai didesnis nei originalaus laikrodžio ciklo.

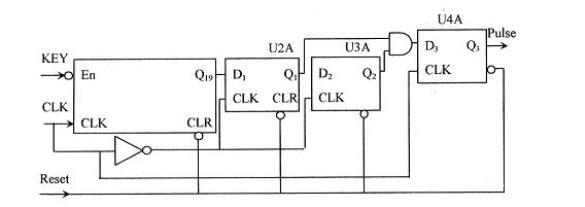

Norint, kad vieno impulso impulsų plotis būtų lygus laikrodžio laikotarpiui, ir tokią pačią fazę kaip ir laikrodžio laikotarpis, 1 paveiksle pavaizduota grandinės konstrukcija yra pagerinta, kaip parodyta 2 paveiksle.

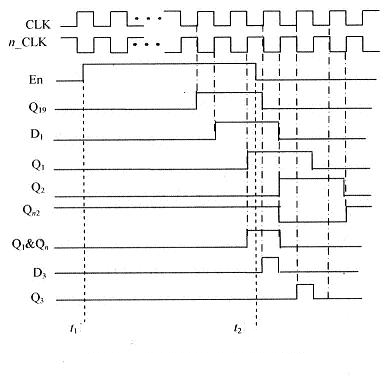

2 paveiksle prieš laikrodį siunčiant į „D flip-flop“, nėra pridedami vartai, kad Q1 terminalas generuoja teigiamą impulsą, sinchronizuotą su NCLK (CLK atvirkštinio impulsų signalas), ir vartų išvestis vienas impulsas, o CLK yra CLK ir CLK yraPusė laikrodžio ciklo skirtumas, nes d įjungimo U4a įvesties d4 d4 kylančiame CLK U4A krašte, kad vieno impulso impulsų plotis būtų toks pat kaip ir laikrodžio ciklas, o vienodo impulsų plotis yrarealizuotas.Ir atidėtas per pusę laikrodžio ciklo, kad išvesties impulsas atitiktų laikrodžio ciklą, kad būtų galima sureguliuoti fazę.Viso vieno impulsų generatoriaus laiko diagrama parodyta 3 paveiksle (3 paveiksle T1 ir T2 yra momentai, kai paspaudžiamas bet kuris raktas, o klavišas pakeliamas).

„Verilog HDL“ kalbos aprašymas, pagrįstas pagrindiniu „Debounce“ skaitikliu ir vieno impulsų generatoriumi pagal FPGA

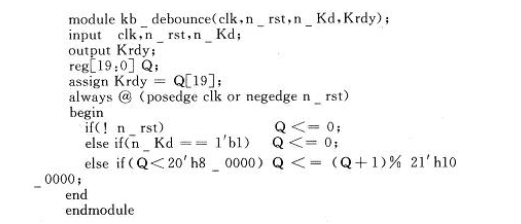

Pagrindinė „Debounce“ skaitiklio grandinė 1 pav., Jos „Verilog HTL“ kalbos kodas, kurį apibūdinti yra taip:

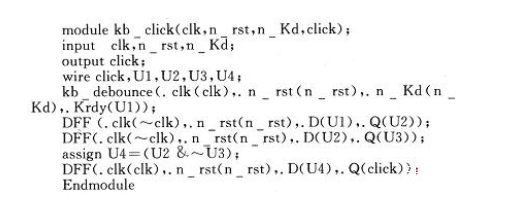

Atstatymas N_RST ir KEY N_KD kode yra aktyvūs žemi.„Verilog HTL“ kalbos kodas, skirtas vieno impulsų generatoriui, yra toks:

„D Flip-Flop DFF“ taip pat naudojamas kode, kodas šiam moduliui įdiegti yra gana paprastas

Išvada

Šis dizainas sėkmingai supažindina su vienkartiniu impulsų generatoriumi sinchroniškai su laikrodžio ciklu, kruopščiai suderintu tiek impulsų pločiu, tiek faze, kad būtų galima išspręsti disponavimo iššūkius.Jo pritaikomumas tęsiasi įvairiausiose FPGA programų spektre, kai paklausa yra tikslūs vieno impulsų išėjimai.„Debounce“ grandinėje demonstruojamas įspūdingas pritaikymas, kad jis atitiktų įvairias FPGA konfigūracijas.Skaitiklis, parengtas atsižvelgiant į konkrečius projekto poreikius, integruoja modulio koregavimus, kad būtų tinkamai tvarkomos skirtingos neryžtingos sąlygos, taip padidindamas programų universalumą.

APIE MUS

Klientų pasitenkinimas kiekvieną kartą.Abipusis pasitikėjimas ir bendrieji interesai.

APIE MUS

Klientų pasitenkinimas kiekvieną kartą.Abipusis pasitikėjimas ir bendrieji interesai.

Funkcijos testas.Aukščiausi ekonomiškai efektyvūs produktai ir geriausia paslauga yra mūsų amžinas įsipareigojimas.

Karštas straipsnis

- LM358 Dvigubo eksploatavimo stiprintuvo išsamus vadovas: „Pinouts“, grandinės schemos, ekvivalentai, naudingi pavyzdžiai

- Ar CR2032 ir CR2016 yra keičiami?

- Suprasti skirtumus ESP32 ir ESP32-S3 Techninės ir veiklos analizė

- Tinkamos baterijos pasirinkimas: AG4, LR626, LR66, 177/376/377, SR626 ir SR626SW ekvivalentų vadovas

- BC547 tranzistorių pagrindai: jungtis, taikymo grandinės, alternatyvūs / papildomi modeliai

- NPN ir PNP: Koks skirtumas?

- ESP32 vs STM32: Kuris mikrovaldiklis jums yra geresnis?

- Kas yra MOSFET ir kaip jis veikia?

- Elektros relės bazė: darbo operacija, tipai ir naudojimas

- PNP tranzistoriai: struktūra, darbo principas ir taikymas

Suprasti programuojamų prietaisų raidą: nuo PAL iki FPGA

Suprasti programuojamų prietaisų raidą: nuo PAL iki FPGA

2024-12-17

SKM800GA176D Semikron PDF duomenų lapas, simbolis, pakuotė

SKM800GA176D Semikron PDF duomenų lapas, simbolis, pakuotė

2024-12-17

Karštos dalies numeris

GJM0335C1ER80BB01D

GJM0335C1ER80BB01D TMK105AC6105KV-F

TMK105AC6105KV-F CGA3E2C0G2A6R8D080AA

CGA3E2C0G2A6R8D080AA GRM0225C1E220GDAEL

GRM0225C1E220GDAEL C1608JB1E334K080AC

C1608JB1E334K080AC CL21B103KBANNWC

CL21B103KBANNWC GRM31MR71C684KA01L

GRM31MR71C684KA01L LD055A680JAB2A

LD055A680JAB2A TPSD107M010R0150

TPSD107M010R0150 F721A227KRC

F721A227KRC

- MTFC8GAKAJCN-4M IT

- IS42S32160A-75BL

- MIC4452YM-TR

- LFE2M50E-6F484C

- MC56F84565VLK

- DS21458N

- MAX6967AEE+T

- FP11073_LISA2-W-CLIP

- V28C24H100BL3

- VE-274-CX

- VI-230-CW-06

- SN74CBTLV3126PW

- T491D336K016AT4814

- LT5400AIMS8E-1#PBF

- T491C106K035AT4513

- PM4329-BGI

- TPS259241DRCR

- STM32L072VZT6

- AM29F080B-55EF

- 793-P-1C-12VDC

- HD64338021A49H

- IDT72255LA15PF

- LC4064V-75T100C5T

- LPC1114FBD48

- MB87D603

- MC68030FE16B

- MK22FN1MOVLQ12

- UPD70F3732GC-8EA-A

- WJLXT905LE

- JTS01-10LT100G

- TG74-1205N1

- Z8S18016VSC/Z180-MPU

- RTL8214FB-CG

- ISPLSI2032VE-300LTN44

- PS8747BQFN40GTR-B1

- LGE3549XSP-P22

- EP4CE30F29C6NG

- VI-910104B

- 348260124